DPD演算性能強(qiáng)化與SoC FPGA在蜂窩網(wǎng)絡(luò)中提升設(shè)備集成度

隨著5G和未來6G蜂窩網(wǎng)絡(luò)的快速發(fā)展,網(wǎng)絡(luò)設(shè)備面臨著更高的性能要求和集成化需求。為了提高設(shè)備的能效和頻譜利用率,數(shù)字預(yù)失真(DPD)演算性能的優(yōu)化成為關(guān)鍵技術(shù)之一。同時(shí),SoC FPGA(片上系統(tǒng)現(xiàn)場(chǎng)可編程門陣列)的應(yīng)用顯著提升了蜂窩網(wǎng)絡(luò)設(shè)備的集成度,為設(shè)備小型化和功耗降低提供了解決方案。

強(qiáng)化DPD演算性能是提升蜂窩網(wǎng)絡(luò)設(shè)備信號(hào)處理能力的重要手段。DPD技術(shù)主要用于補(bǔ)償功率放大器(PA)的非線性失真,以保證信號(hào)傳輸質(zhì)量。在傳統(tǒng)系統(tǒng)中,DPD算法往往依賴于軟件實(shí)現(xiàn),這可能導(dǎo)致延遲較高和計(jì)算資源浪費(fèi)。通過優(yōu)化DPD演算性能,例如采用硬件加速方法或高效的算法結(jié)構(gòu),可以顯著提高處理速度并降低功耗。研究表明,強(qiáng)化后的DPD演算能夠在高帶寬場(chǎng)景下實(shí)現(xiàn)更精準(zhǔn)的失真補(bǔ)償,從而提升整體網(wǎng)絡(luò)吞吐量和設(shè)備可靠性。

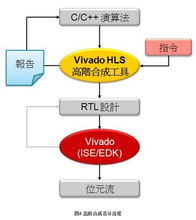

SoC FPGA在蜂窩網(wǎng)絡(luò)設(shè)備中的應(yīng)用極大地促進(jìn)了集成度的提升。SoC FPGA結(jié)合了FPGA的可編程邏輯與處理器核心,支持高度定制化的硬件設(shè)計(jì)。這允許網(wǎng)絡(luò)設(shè)備將多個(gè)功能模塊(如基帶處理、信號(hào)調(diào)制解調(diào)及DPD運(yùn)算)集成到單一芯片中。相比于傳統(tǒng)的分立組件方案,SoC FPGA減少了物理尺寸和系統(tǒng)復(fù)雜性,同時(shí)提高了數(shù)據(jù)處理效率。例如,在小型基站或移動(dòng)終端中,SoC FPGA可以實(shí)現(xiàn)信號(hào)鏈路的無縫集成,從而降低設(shè)備成本、縮短開發(fā)周期,并增強(qiáng)系統(tǒng)的可擴(kuò)展性。

DPD演算性能強(qiáng)化與SoC FPGA的結(jié)合,為蜂窩網(wǎng)絡(luò)設(shè)備帶來了協(xié)同效應(yīng)。通過將強(qiáng)化后的DPD算法部署于SoC FPGA的硬件加速器中,可以實(shí)現(xiàn)實(shí)時(shí)信號(hào)處理和低功耗運(yùn)行。這種集成化解決方案不僅提高了設(shè)備的能效比,還為未來網(wǎng)絡(luò)升級(jí)(如毫米波通信)提供了技術(shù)基礎(chǔ)。實(shí)際應(yīng)用中,許多電信設(shè)備制造商已采用這種方案,以應(yīng)對(duì)日益增長(zhǎng)的數(shù)據(jù)流量和多樣化服務(wù)需求。

強(qiáng)化DPD演算性能與SoC FPGA的應(yīng)用是推動(dòng)蜂窩網(wǎng)絡(luò)設(shè)備演進(jìn)的關(guān)鍵方向。通過優(yōu)化算法和提升集成度,網(wǎng)絡(luò)設(shè)備能夠在性能、功耗和成本之間實(shí)現(xiàn)更好的平衡。未來,隨著人工智能和邊緣計(jì)算的融入,這些技術(shù)將進(jìn)一步推動(dòng)蜂窩網(wǎng)絡(luò)向更高效率、更智能化的方向發(fā)展。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.tschache.cn/product/23.html

更新時(shí)間:2026-04-16 04:24:39